Indexed In

- Open J Gate

- Genamics JournalSeek

- Academic Keys

- JournalTOCs

- ResearchBible

- China National Knowledge Infrastructure (CNKI)

- Scimago

- Ulrich's Periodicals Directory

- Electronic Journals Library

- RefSeek

- Hamdard University

- EBSCO A-Z

- OCLC- WorldCat

- SWB online catalog

- Virtual Library of Biology (vifabio)

- Publons

- MIAR

- Scientific Indexing Services (SIS)

- Euro Pub

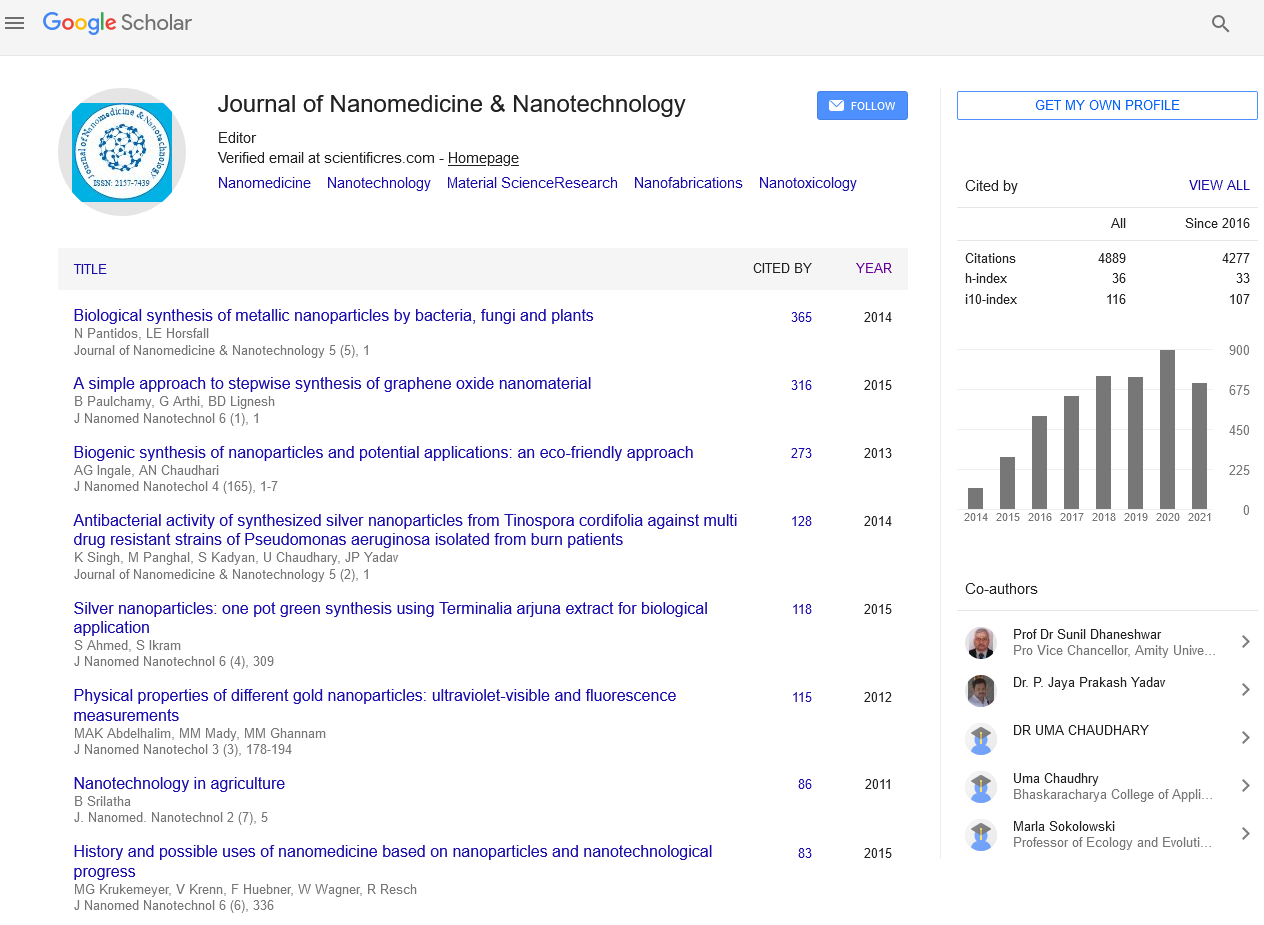

- Google Scholar

Useful Links

Share This Page

Journal Flyer

Open Access Journals

- Agri and Aquaculture

- Biochemistry

- Bioinformatics & Systems Biology

- Business & Management

- Chemistry

- Clinical Sciences

- Engineering

- Food & Nutrition

- General Science

- Genetics & Molecular Biology

- Immunology & Microbiology

- Medical Sciences

- Neuroscience & Psychology

- Nursing & Health Care

- Pharmaceutical Sciences

ALD versus non-ALD nanomaterials for low-power charge trapping memory devices

World Congress on Nanoscience and Nanotechnology

October 16-17, 2017 Dubai, UAE

Ammar Nayfeh and Nazek El-Atab

Masdar Institute of Science and Technology, UAE

Posters & Accepted Abstracts: J Nanomed Nanotechnol

Abstract:

In the past few decades, the demand for low power and high-density memory devices has increased drastically due to the growing market of consumer electronic equipment such as cellular phones, digital cameras, laptops, etc. This is driving the need to continue scaling down the memory devices. However, the traditional way of scaling these devices is reaching physical limitations such as short channel effects and a very high electric-field across the tunnel oxide leading to its breakdown. Therefore, the introduction of nanomaterials within memory devices is crucial to be able to further scale them down and reduce their operating voltages without degrading their performance. In this work, the fabrication and characterization of charge trapping memory devices with a charge trapping layer of nano-islands grown by Atomic Layer Deposition (ALD): Zirconia (ZrO2) and Zinc-Oxide (ZnO) vs. nanomaterials synthesized by non-ALD methods and which are spin-coated/ drop-casted on the sample: 2.85 nm Si nanoparticles, 1-5 nm ZnO nanoparticles and Quattro-layer graphene nano-platelets are demonstrated and compared. This work explains the effect of the different electronic properties of the nanomaterials on the measured performance of the memory devices using C-V measurements. The high electron-affinity of the materials allows the stored electrons to be well confined in a deep quantum well and therefore an improved retention characteristic would be obtained. In addition, nanomaterials with a higher-κ result in an increased injection electric-field which would cause a larger memory window at a lower operating-voltage. Finally, the growth of the nanomaterials for charge trapping layer by ALD allows the deposition of the active layer of the memory by a single ALD-step which would reduce the contamination probability since the device does not need to be transferred to different tools for the deposition of the active layer. This will result in a lower time of fabrication and therefore lower-cost.